dsp器件按设计要求可以分为两类。第一类,应用领域为廉价的、大规模嵌入式应用系统,如手机、磁盘驱动(dsp用作伺服电机控制)以及便携式数字音频播放器等。在这些应用中价格和集成度是最重要的考虑因素。对于便携式电池供电的设备,功耗也是一个关键的因素。尽管这些应用常常需要开发运行于dsp的客户应用软件和外围支持硬件,但易于开发的要求仍然是次要的因素,因为批量生产可以分摊开发成本,从而降低单位产品的开发成本。

另外一类是需要用复杂算法对大量数据进行处理的应用,例如声纳探测和地震探测等,也需要用dsp器件。该类设备的批量一般较小、算法要求苛刻、产品很大而且很复杂。所以设计工程师在选择处理器时会尽量选择性能最佳、易于开发并支持多处理器的dsp器件。有时,设计工程师更喜欢选用现成的开发板来开发系统而不是从零开始硬件和软件设计,同时可以采用现成的功能库文件开发应用软件。

在实际设计时应根据具体的应用选择合适的dsp。不同的dsp有不同的特点,适用于不同的应用,在选择时可以遵循以下要点。

算法格式 dsp的算法有多种。绝大多数的dsp处理器使用定点算法,数字表示为整数或-1.0到+1.0之间的小数形式。有些处理器采用浮点算法,数据表示成尾数加指数的形式:尾数×2指数。

浮点算法是一种较复杂的常规算法,利用浮点数据可以实现大的数据动态范围(这个动态范围可以用最大和最小数的比值来表示)。浮点dsp在应用中,设计工程师不用关心动态范围和精度一类的问题。www.11665.coM浮点dsp比定点dsp更容易编程,但是成本和功耗高。

由于成本和功耗的原因,一般批量产品选用定点dsp。编程和算法设计人员通过分析或仿真来确定所需要的动态范围和精度。如果要求易于开发,而且动态范围很宽、精度很高,可以考虑采用浮点dsp。

也可以在采用定点dsp的条件下由软件实现浮点计算,但是这样的软件程序会占用大量处理器时间,因而很少使用。有效的办法是“块浮点”,利用该方法将具有相同指数,而尾数不同的一组数据作为数据块进行处理。“块浮点”处理通常用软件来实现。

数据宽度 所有浮点dsp的字宽为32位,而定点dsp的字宽一般为16位,也有24位和20位的dsp,如摩托罗拉的dsp563xx系列和zoran公司的 zr3800x系列。由于字宽与dsp的外部尺寸、管脚数量以及需要的存储器的大小等有很大的关系,所以字宽的长短直接影响到器件的成本。字宽越宽则尺寸越大,管脚越多,存储器要求也越大,成本相应地增大。在满足设计要求的条件下,要尽量选用小字宽的dsp以减小成本。

在关于定点和浮点的选择时,可以权衡字宽和开发复杂度之间的关系。例如,通过将指令组合连用,一个16位字宽的dsp器件也可以实现32位字宽双精度算法(当然双精度算法比单精度算法慢得多)。如果单精度能满足绝大多数的计算要求,而仅少量代码需要双精度,这种方法也可行,但如果大多数的计算要求精度很高,则需要选用较大字宽的处理器。

请注意,绝大多数dsp器件的指令字和数据字的宽度一样,也有一些不一样,如adi(模拟器件公司)的adsp-21xx系列的数据字为16位而指令字为24位。

dsp的速度 处理器是否符合设计要求,关键在于是否满足速度要求。测试处理器的速度有很多方法,最基本的是测量处理器的指令周期,即处理器执行最快指令所需要的时间。指令周期的倒数除以一百万,再乘以每个周期执行的指令数,结果即为处理器的最高速率,单位为每秒百万条指令mips。

但是指令执行时间并不能表明处理器的真正性能,不同的处理器在单个指令完成的任务量不一样,单纯地比较指令执行时间并不能公正地区别性能的差异。现在一些新的dsp采用超长指令字(vliw)架构,在这种架构中,单个周期时间内可以实现多条指令,而每个指令所实现的任务比传统dsp少,因此相对vliw和通用dsp器件而言,比较mips的大小时会产生误导作用。

即使在传统dsp之间比较mips大小也具有一定的片面性。例如,某些处理器允许在单个指令中同时对几位一起进行移位,而有些dsp的一个指令只能对单个数据位移位;有些dsp可以进行与正在执行的alu指令无关的数据的并行处理(在执行指令的同时加载操作数),而另外有些dsp只能支持与正在执行的alu指令有关的数据并行处理;有些新的dsp允许在单个指令内定义两个mac。因此仅仅进行mips比较并不能准确得出处理器的性能。

解决上述问题的方法之一是采用一个基本的操作(而不是指令)作为标准来比较处理器的性能。常用到的是mac操作,但是mac操作时间不能提供比较dsp性能差异的足够信息,在绝大多数dsp中,mac操作仅在单个指令周期内实现,其mac时间等于指令周期时间,如上所述,某些dsp在单个mac周期内处理的任务比其它dsp多。mac时间并不能反映诸如循环操作等的性能,而这种操作在所有的应用中都会用到。

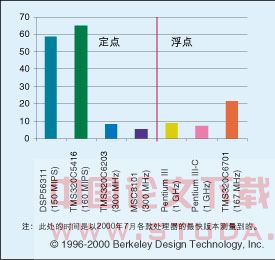

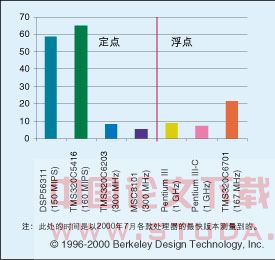

最通用的办法是定义一套标准例程,比较在不同dsp上的执行速度。这种例程可能是一个算法的“核心”功能,如fir或iir滤波器等,也可以是整个或部分应用程序(如语音编码器)。图1为使用bdti公司的工具测试的几款dsp器件性能。

在比较dsp处理器的速度时要注意其所标榜的mops(百万次操作每秒)和mflops(百万次浮点操作每秒)参数,因为不同的厂商对“操作”的理解不一样,指标的意义也不一样。例如,某些处理器能同时进行浮点乘法操作和浮点加法操作,因而标榜其产品的mflops为mips的两倍。

其次,在比较处理器时钟速率时,dsp的输入时钟可能与其指令速率一样,也可能是指令速率的两倍到四倍,不同的处理器可能不一样。另外,许多dsp具有时钟倍频器或锁相环,可以使用外部低频时钟产生片上所需的高频时钟信号。

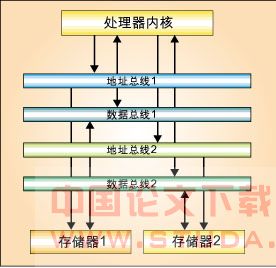

存储器管理 dsp的性能受其对存储器子系统的管理能力的影响。如前所述,mac和其它一些信号处理功能是dsp器件信号处理的基本能力,快速mac执行能力要求在每个指令周期从存储器读取一个指令字和两个数据字。有多种方法实现这种读取,包括多接口存储器(允许在每个指令周期内对存储器多次访问)、分离指令和数据存储器(“哈佛”结构及其派生类)以及指令缓存(允许从缓存读取指令而不是存储器,从而将存储器空闲出来用作数据读取)。图2和图3显示了哈佛存储器结构与很多微控制器采用的“冯・诺曼”结构的差别。

另外要注意所支持的存储器空间的大小。许多定点dsp的主要目标市场是嵌入式应用系统,在这种应用中存储器一般较小,所以这种dsp器件具有小到中等片上存储器(4k到64k字左右),备有窄的外部数据总线。另外,绝大多数定点dsp的地址总线小于或等于16位,因而可外接的存储器空间受到限制。

一些浮点dsp的片上存储器很小,甚至没有,但外部数据总线宽。例如ti公司的tms320c30只有6k片上存储器,外部总线为24位,13位外部地址总线。而adi的adsp2-21060具有4mb的片上存储器,可以多种方式划分为程序存储器和数据存储器。

选择dsp时,需要根据具体应用对存储空间大小以及对外部总线的要求来选择。

开发的简便性 对不同的应用来说,对开发简便性的要求不一样。对于研究和样机的开发,一般要求系统工具能便于开发。而如果公司在开发下一代手机产品,成本是最重要的因素,只要能降低最终产品的成本,一般他们愿意承受很烦琐的开发,采用复杂的开发工具 (当然如果大大延迟了产品上市的时间则是另一回事)。

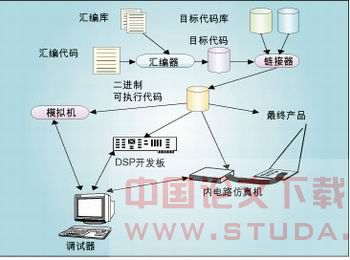

因此选择dsp时需要考虑的因素有软件开发工具(包括汇编、链接、仿真、调试、编译、代码库以及实时操作系统等部分)、硬件工具(开发板和仿真机)和高级工具(例如基于框图的代码生成环境)。利用这些工具的设计过程如图4所示。

选择dsp器件时常有如何实现编程的问题。一般设计工程师选择汇编语言或高级语言(如c或ada),或两者相结合的办法。现在大部分的dsp程序采用汇编语言,由于编译器产生的汇编代码一般未经最优化,需要手动进行程序优化,降低程序代码大小和使流程更合理,进一步加快程序的执行速度。这样的工作对于消费类电子产品很有意义,因为通过代码的优化能弥补dsp性能的不足。

使用高级语言编译器的设计工程师会发现,浮点dsp编译器的执行效果比定点dsp好,这有几个原因:首先,多数的高级语言本身并不支持小数算法;其次,浮点处理器一般比定点处理器具有更规则的指令,指令限制少,更适合编译器处理;第三,由于浮点处理器支持更大的存储器,能提供足够的空间。编译器产生的代码一般比手动生成的代码更大。

不管是用高级语言还是汇编语言实现编程,都必须注意调试和硬件仿真工具的使用,因为很大一部分的开发时间会花在这里。几乎所有的生产商都提供指令集仿真器,在硬件完成之前,采用指令集仿真器对软件调试很有帮助。如果所用的是高级语言,对高级语言调试器功能进行评估很重要,包括能否与模拟机和/或硬件仿真器一起运行等性能。

大多数dsp销售商提供硬件仿真工具,现在许多处理器具有片上调试/仿真功能,通过采用ieee1149.1jtag标准的串行接口访问。该串行接口允许基于扫描的仿真,即程序员通过该接口加载断点,然后通过扫描处理器内部寄存器来查看处理器到达断点后寄存器的内容并进行修改。

很多的生产商都可以提供现成的dsp开发系统板。在硬件没有开发完成之前可用开发板实现软件实时运行调试,这样可以提高最终产品的可制造性。对于一些小批量系统甚至可以用开发板作为最终产品电路板。

支持多处理器 在某些数据计算量很大的应用中,经常要求使用多个dsp处理器。在这种情况下,多处理器互连和互连性能(关于相互间通信流量、开销和时间延迟)成为重要的考虑因素。如adi的adsp-2106x系列提供了简化多处理器系统设计的专用硬件。

电源管理和功耗 dsp器件越来越多地应用在便携式产品中,在这些应用中功耗是一个重要的考虑因素,因而dsp生产商尽量在产品内部加入电源管理并降低工作电压以减小系统的功耗。在某些dsp器件中的电源管理功能包括: a. 降低工作电压:许多生产商提供低电压dsp版本(3.3v,2.5v,或1.8v),这种处理器在相同的时钟下功耗远远低于5v供电的同类产品。

b. “休眠”或“空闲”模式:绝大多数处理器具有关断处理器部分时钟的功能,降低功耗。在某些情况下,非屏蔽的中断信号可以将处理器从“休眠”模式下恢复,而在另外一些情况下,只有设定的几个外部中断才能唤醒处理器。有些处理器可以提供不同省电功能和时延的多个“休眠”模式。

c. 可编程时钟分频器:某些dsp允许在软件控制下改变处理器时钟,以便在某个特定任务时使用最低时钟频率来降低功耗。

d. 外围控制:一些dsp器件允许程序停止系统未用到的外围电路的工作。

不管电源管理特性怎么样,设计工程师要获得优秀的省电设计很困难,因为dsp的功耗随所执行的指令不同而不同。多数生产商所提供的功耗指标为典型值或最大值,而ti公司给出的指标是一个例外,该公司的应用实例中详细地说明了在执行不同指令和不同配置下的功耗。

成本因素 在满足设计要求条件下要尽量使用低成本dsp,即使这种dsp编程难度很大而且灵活性差。在处理器系列中,越便宜的处理器功能越少,片上存储器也越小,性能也比价格高的处理器差。

封装不同的dsp器件价格也存在差别。例如,pqfp和tqfp封装比pga封装便宜得多。

在考虑到成本时要切记两点。首先,处理器的价格在持续下跌;第二点,价格还依赖于批量,如10,000片的单价可能会比1,000片的单价便宜很多。

本文小结 dsp处理器存在两种发展趋势:一是dsp应用越来越多,如手机和便携式音频播放器等。dsp将集成更多功能,如a/d转换、lcd控制器等,系统成本和器件数将会大为降低。另一个趋势是将dsp作为ip出售,如亿恒科技公司的camel和tricore内核。随着eda工具的不断成熟,系统设计工程师将更容易地修改dsp内核,加入用户专用外围电路以实现更专业化、更低成本的dsp解决方案。